## PROVA SCRITTA DI ELETTRONICA

Prof. Luca Salvini

3a Ae Nome \_\_\_\_\_\_ 16/05/2006

Con la presente prova si intende verificare il raggiungimento dei seguenti obiettivi:

- Ob.9 saper analizzare e progettare un piccolo sistema sequenziale SSI

- Ob.10 saper disegnare la temporizzazione in/out di un sistema combinatorio o sequenziale

- Ob.11 saper analizzare e progettare un piccolo sistema sequenziale e MSI;

- Ob.13 saper progettare funzioni combinatorie con ROM

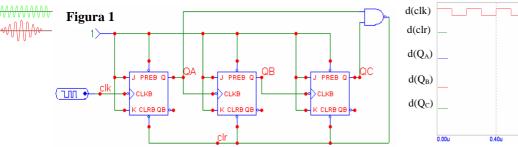

- 1. Sia dato il dispositivo in figura 1. Completa il diagramma temporale, indicando le uscite  $Q_A$ ,  $Q_B$  e  $Q_C$  (inizialmente basse), l'ingresso clr1 (inizialmente alto) e disegnandone l'andamento (i FF sono di tipo NET con ingressi di clear e preset attivi bassi).

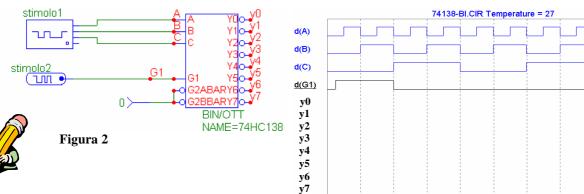

2. Sia dato il dispositivo combinatorio in figura 2. Gli ingressi A, B, C e G1 seguono l'andamento riportato in figura 2. Completa il diagramma temporale, disegnando l'andamento delle uscite.

0.00u

0.40u

0.80u

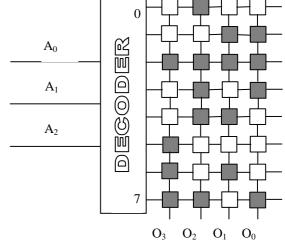

3. Considera la matrice ROM **8x4** nella figura a destra e riporta in una tabella le parole contenute in memoria ed i relativi indirizzi. Una cella **piena** (scura) individua uno **0** ed una cella **vuota** (bianca) un **1**.

1.20u

2.00u

1.60u

- 4. Costruisci la matrice **ROM 5x6** necessaria per realizzare una tabella di programmazione in grado di fornire un'uscita binaria pari a (x³-8x+9), essendo l'ingresso x un numero decimale da 0 a 4 codificato in binario. Rappresenta gli uni con celle vuote (bianche) e gli zeri con celle piene (scure).

- 5. Progetta un divisore di frequenza per **2048** utilizzando contatori binari integrati (modulo 10 o modulo 16, con possibilità di sequenza di conteggio trancata); disegna, illustrandolo, lo schema dei collegamenti.

- 6. Disegna le forme d'onda degli ingressi e di tutte le uscite  $Q_i$  di uno shift register PIPO a 4 bit, che inizialmente deve essere presettato su 3; è presente un ingresso  $SH/\overline{LD}$  (shift/load).