## PROVA SCRITTA DI *ELETTRONICA*

Prof. Luca Salvini

3Bt Nome 26/05/09

Con la presente prova si intende verificare il raggiungimento dei seguenti obiettivi:

Ob.9. saper analizzare e progettare un piccolo sistema sequenziale SSI

Ob.10. saper disegnare la temporizzazione in/out di un sistema combinatorio o sequenziale

Ob.11. saper analizzare e progettare un piccolo sistema sequenziale MSI

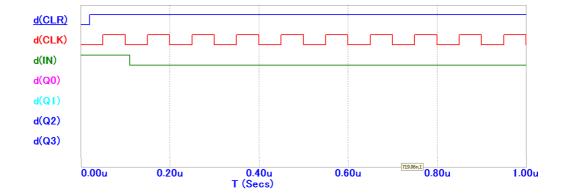

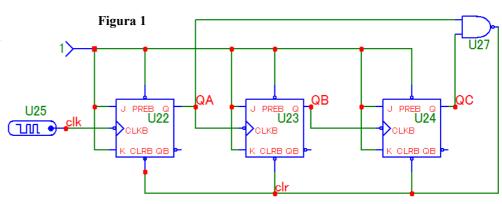

1. Sia dato il dispositivo in Fig. 1. Completa il diagramma temporale, indicando le uscite  $Q_A$ ,  $Q_B$  e  $Q_C$  (inizialmente basse), l'ingresso clr di clear basso) e disegnandone l'andamento (i FF sono NET di tipo con ingressi clear di

preset attivi bassi).

- 2. Progetta un contatore sincrono modulo 4 (conteggio da 0 a 3), realizzato mediante Flip Flop JK.

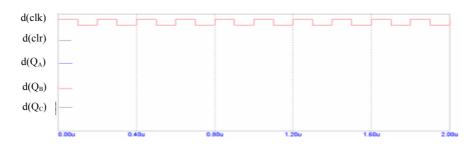

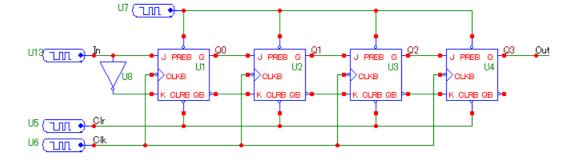

- 3. Disegna la temporizzazione delle uscite (Q<sub>i</sub>) del dispositivo la cui struttura interna è riportata in Fig. 2, in funzione della temporizzazione degli ingressi di Fig. 3. Di che tipo di dispositivo si tratta?

Figura 3